### Design and Implementation of Convolutional Encoder and Viterbi Decoder Using FPGA.

Riham Ali ZbaidKasim K. AbdallaDepartment of Electrical Engineering/Faculty of Engineering/ University of Babylon<br/>ralialibadi@gmail.comkasimkaa.11@gmail.com

### Abstract

Keeping the fineness of data is the most significant thing in communication. There are many factors that affect the accuracy of the data when it is transmitted over the communication channel such as noise etc. to overcome these effects are encoding channels encryption. In this paper is used for one type of channel coding is convolutional codes. Convolution encoding is a Forward Error Correction (FEC) method used in incessant one-way and real time communication links . It can offer a great development in the error bit rates so that small, low energy, and devices cheap transmission when used in applications such as satellites. In this paper highlight the design, simulation and implementation of convolution encoder and Viterbi decoder by using MATLAB- program (2011). SIMULINK HDL coder is used to convert MATLAB-SIMULINK models to VHDL using plates Altera Cyclone II code DE2-70. Simulation and evaluation of the implementation of the results coincided with the results of the design show the coinciding with the designed results.

Keywords:- Convolutional encoder, Viterbi decoder, MATLAB-Program, FPGA.

#### الخلاصة

الحفاظ على دقة البيانات هو الشيء الأكثر أهمية في مجال الاتصالات. هناك العديد من العوامل التي تؤثر على دقة البيانات عندما يتم نقلها عبر قناة الاتصال مثل الضوضاء الخلل تغلب على هذه الاثار يتم تشفير قنوات الترميز. في هذه الورقة يتم استخدام نوع واحد من قناة الترميز هي رموز التلافيف على وجه التحديد. ترميز الالتواء هو أسلوب خطأ إلى الأمام تصحيح (FEC) المستخدمة في وصلات الاتصالات في الوقت الحقيقي المتواصلة في اتجاه واحد التي يمكن أن تقدم تطورا كبيرا في معدلات الخطأ بت وهكذا تكون صغيرة ومنخفضة الطاقة وأجهزة الإرسال الرخيصة عند استخدامها في تطبيقات مثل الأقمار الصناعية. في هذه الورقة تسليط الضوء على تصميم ومحاكاة وتنفيذ التشفير التلافيف وفك فيتربي باستخدام المي المقار (٢٠١١). يستخدم للمال المار المعرمج لتحويل نماذج SIMULINK وتنفيذ التشفير التلافيف وفك فيتربي ماستخدام لوحات ألتيرا الصناعية. المقدم المال المار مع يتحويل نماذج محاكاة وتنفيذ التشفير التلافيف وفك فيتربي باستخدام المناعية. ومنا الالت المقاد من المال المار مع المالة واحد التي يمكن أن تقدم تطورا كبيرا في الصناعية. ومنا المقادر المالغ المار مع ليوات المالة واحمالة وأجهزة الإرسال الرخيصة عند استخدامها في تطبيقات مثل المناعية. ومالا المارة منابع الضوء على تصميم ومحاكاة وتنفيذ التشفير التلافيف وفك فيتربي باستخدام الوحات ألتيرا المناعية. المقدم المارقة تسليط الضوء على تصميم ومحاكاة وتنفيذ التشوير التلافيف ونك فيتربي باستخدام الوحات ألتيرا الملام المالي المالي المالي الموحات الموحات التيربي، MATLAB التي رمز ADL المالي الموحات ألتيرال الموحات ألتيرا المالي المالياني المالي المولي الموحات المالي اللالي المالي المالي المالي المالي المالي المالي ال

### 1. Introduction

In telecommunication and information theory, channel codinghas been used to improve the quality of data transmission. To improve the performance of communication system, there are various numbers of techniques channel coding deals with. Channel coding increases the data transmission rate at a fixed error rate or error rate can be reduced with a fixed data transmission rate in digital communication systems. The maximum performance of data transmission is restricted by Shannon limit [Sh,1948]. There are two basic errors correcting schemes the first one is FEC (the errors can be corrected automatically on its occurrence)and the second is Automatic Repeat Request (ARQ) (using stop-and-wait protocol, where the message is requested to retransmit whenever error is detected) have been employed in communications systems [Calhan *et al.*,2007]. Choice one of these schemes depend on the application.

As an alternative to block codes, Elias in 1955[Vamshi,2005] introduced convolution codes. Convolutional codes perform encoding on serial data, one or a few bits at a time, while block codes perform encoding on relatively large message blocks. Compareing with the block coding, convolutional encoding performance is better error correction although it requires an extensive memory in decoding [Wayal *et*

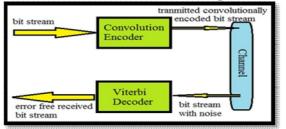

*al.*,2015]. One of the FEC schemes is convolutional encoding which is used for the channel coding in digital communication systems as shown in Figure 1. The convolutional encoding technique is a strategy widely employed in numerous applications in order to achieve reliable data transmission, including radio, digital video, satellite communication andmobile communication [Kolakaluri *et al.*,2015].

Figure 1. FEC Architecture

A convolution encoders are usually characterized in (n, k, m) format where n represents the number of outputs of bits of the encoder; k is the number of inputs of bits of the encoder and m is the number of memory elements. The organization of convolutional encoder is calculated in terms of rate code. The code rate is the ratio of input to output information in an encoder (k/n).Some further format of convolutional code chips indicate the three factors of code by (n, k, L), where L is the constraint length of thecode and defined as: L= m+1[Pednekar *et al.*,2013].Convolutional encoder is decoded by Viterbi Algorithm (VA) or Maximum A Postoriory (MAP) algorithm.For constraint length L<5, VA is used and for L>5MAP algorithm is employed [Maiya *et al.*, 2012].VA is the most resource consuming, efficient and robust.

### 2. Convolutional Encoder and Viterbi Decoder Description.

A convolutional encoders is an instrument, where the output is a function of they currents state nand they current input. It consists of one nor more D flip flop and multiple Exclusive-OR gates. Exclusive-OR gates are joined to some stage of a number of shift registers memory and to the current input to form the output npolynomials[Calhan *et al.*,2007]. The model used to form the coded output data can be designed as binary strings so called Generator Polynomials (GP)[ Wayal *et al*,2015]. A convolution encoder is described with the help of state table, state ndiagramnand trellis diagram[Kumawat *et al.*,2012]. There are different forms of convolutional encoding which convey different requirements to the decoder.

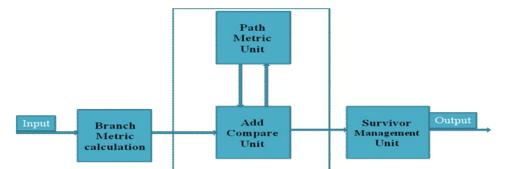

Based on the maximum likelihood algorithm, in 1967 A.J. Viterbi devised and analyzed Viterbi decoding [Mceliece *et al.*,1996].VA is a decoding process for convolutional codesnand it nuses maximum likelihood decoding ntechnique due to it is the most optimal algorithm for decoding of a convolution code [Sudharani *et al.*,2015; Dhanda *et al.*,2014]. Trellis diagram has been used to describe convolutional encoded data and Viterbi decodeddata at the receiver's end. VA has encoded knowledge of convolutional data and that enables it to perform its decoding[Sudharani *et al.*,2015].The difference of the number of bits between the received symbol bits at the decoder and the sent symbol bits from the encoder is defined as Hamming distance[Shukla *et al.*,2014]. Soft decision Viterbi decoding determines the distance between the observed symbol and the probable sent symbol and discoversoriginal bits. The basic performance of the viterbi decoder is branch metric, path calculation and survivor management unit[Selvi *et al.*,2015]. The architecture of the viterbi decoder is illustrated in Figure 2.

Figure 2. Viterbi decoder Basic building blocks [Shukla ,2014].

### 3. Design and Simulation of Convolutional Encoder and Viterbi Decoder Using MATLAB

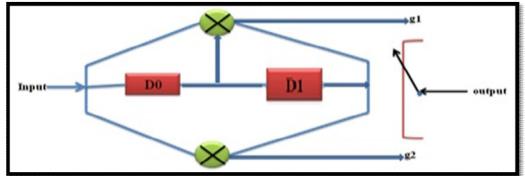

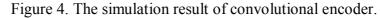

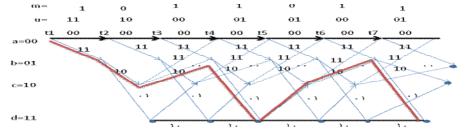

The describe of the structure for convolutional encoder with rate[1/2] and code generators [7,5] is used. Figure 3 shows the structure for convolutional encoder. Table 1 shows the calculation of output bits for described convolutional encoder which has constraint length of 3 when input message is 1011011. Figure 4 shows the simulation result of convolutional encoder without flushing bits. The simulation result observes that the output bits are 11100001010001.Figure 5describes the trellis diagram of convolution encoder. Figure 6shows communication system with the simulation result of viterbi decoder. In order to verify the simulation results for convolutional encoder and viterbi decoder two cases are used. The calculated results show the coincidence with simulation results.

Figure 3. The structure for convolutional encoder.

| Input                 | Modulo 2 Adder Outputs |             |

|-----------------------|------------------------|-------------|

|                       | $g_1 = 111$            | $g_2 = 101$ |

| 1                     | 1                      | 1           |

| 0                     | 1                      | 0           |

| 1                     | 0                      | 0           |

| 1                     | 0                      | 1           |

| 0                     | 0                      | 1           |

| 1                     | 0                      | 0           |

| 1                     | 0                      | 1           |

| Output=11100001010001 |                        |             |

Figure 5. The trellis diagram of convolution encoder.

Figure 6. The simulation result of viterbi decoder.

# 4. The Register Transfer Level (RTL) implementation of Convolutional Encoder and Viterbi Decoder based on FBGA.

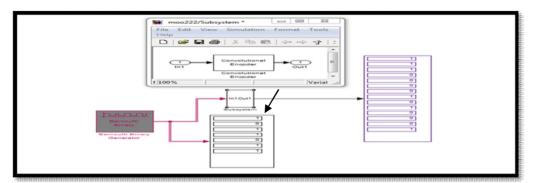

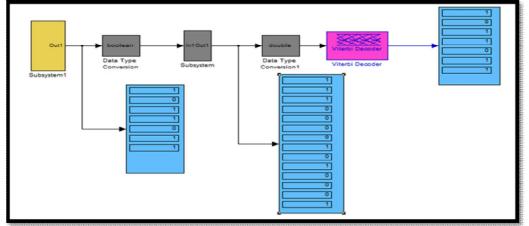

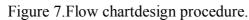

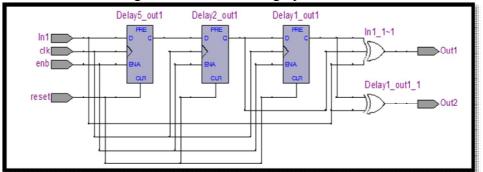

Figure (7)describes the procedure the design and implementation technique used .To perform the convolutional encoder and Viterbi decoder implementation RTL program has been used. Figure (8) describes the RTL implementation of the convolutional encoder based on FBGA. Figure (9) describes the RTL implementation of the viterbi decoder basedbased on FBGA.

Figure 8. The RTL implementation of the convolutional encoder baseds on FPGAs.

Figure 9.The RTL implementation of the viterbi decoder units based on FPGAs.

## **5**. Simulation of Convolutional Encoder and Viterbi Decoder based on Modelsim using FBGA.

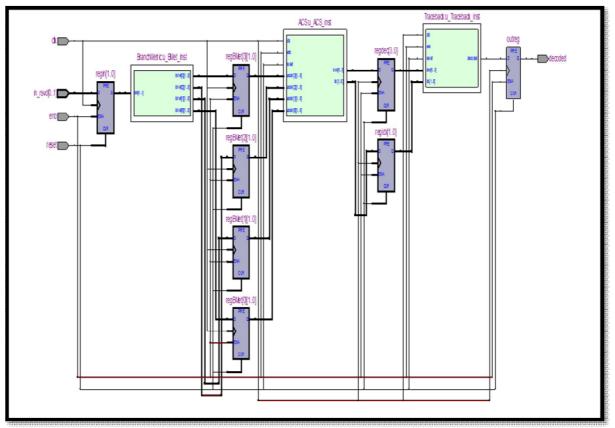

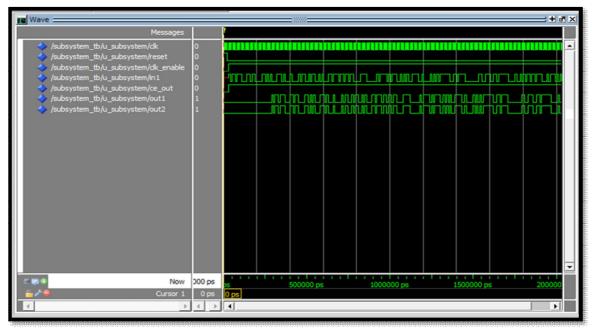

Modelsim program is used to test the results of matlab simulation. Figure (10) shows the input and output signals for convolutional encoder with a rate of [1/2] based on FBGA. Figure (11) shows the input and output signals for Viterbi decoder based on FBGA.

Figure 10.A rate of 1/2 convolutional encoder.

#### Journal of Babylon University/Pure and Applied Sciences/ Vol.(26), No.(3), 2018

Figure 11. The input and output signals for viterbi decoder

### **6.**Conclusions

Forward error correction (FEC) codes are an essential part of the digital communication systems. Convolutional codes are used symbols to perform encoding technology. The Viterbi algorithm has proven to be a powerful tool in the decoding technique for Convolutional codes. As well as MATLAB simulink has proved its ability to design and verify convolutional encoder and viterbi decoder. FPGA proven to be effective mechanism for the implementation of the system where it was send a signal after encoded using Convolutional codes and receiving and decoding using Viterbi algorithm.the simulation results confirm that the signal is received without the occurrence of errors in the transmitted signal, which provides FPGA high speed, and high level of integration, low development costs and require low energy.

Trade shows Oltara- CYCLON several DE2-70 second FPGA family is cabability efforts to implement the verification of the proposed system performance evaluation.

### **7.References**

- Calhan, A.,2007, CelalCeken and Ismail Ertruk, "Comparative Performance Analysis of Forward Error correction Techniques used in Wireless Communications", Proceedings of the third International Conference on wireless and Mobile Communications,0-7695-2796-5/07.

- Sudharani, B. K., Dhananjay, B. K., Praveen, J., Rao, A. R., 2015, "Efficient Convolutional Adaptive Viterbi Encoder and Decoder Using Verilog", International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering, Vol. 3, Issue.1, April.

- Sudharani, B. K., Dhananjay, B., Praveen, J., Rao, A. R., 2015, "Efficient Convolutional Adaptive Viterbi Encoder and Decoder Using RTL Design", International Journal of Innovative Research in Electrical, Electronics, Instrumentation and Control Engineering, Vol. 3, Issue. 2, February .

- Kumawat, H. L., Sharma, S.,2012, "An Implementation of a Forward Error Correction Technique using Convolution Encoding with Viterbi Decoding", International Journal of Soft Computing and Engineering (IJSCE), Vol. 2, Issue. 5, November.

### Journal of Babylon University/Pure and Applied Sciences/ Vol.(26), No.(3), 2018

- Selvi, K. P., Roselin, J. J. A., 2015, "Design and Implementation of Convolution Encoder and Viterbi Decoder Using FPGA", International Journal of Innovative Research in Computer and Communication Engineering, Vol. 3, Special Issue 1, February.

- Wayal, K., Gore, K., Waikule, S., Wagaj, S. C., 2015, "Convolutional Encoding and Viterbi Decoding Based on FPGA Using VHDL", International Journal of Advanced Technology in Engineering and Science, Vol. 03, Issue. 01, January.

- VamshiMalladi, M., 2005, "Reconfigurable Viterbi Decoder", The University of New Brunswick, Canada.

- Kolakaluri, P., Suryaprakash, R., Vijaybhaska, B., 2012-2015, "HDL Implementation of convolution encoder and viterbi decoder", International Journal of Engineering Research & Technology (IJERT), Vol. 1 Issue 5, July.

- Mceliece, R. J., 1996, Fellow, IEEE and Wei Lin, student member, IEEE, "The trellis complexity of Convolutional Codes", IEEE Transactions on Information Theory, Vol. 42, No. 6, November.

- Pednekar, R. M., Dayanand, B. M.,2013, "Design and Implementation of Convolution Encoder with Viterbi Decoder", International Journal of Emerging Technologies in Computational and Applied Sciences (IJETCAS), pp. 84-89, September-November.

- Dhanda, S., Azizullah, T. A. M., 2014, "Performance Assessment of Convolution Codes withdifferent modulation technique", International Journal of Engineering and Innovative Technology (IJEIT), Vol. 3, Issue. 12, June.

- Shukla, S., Sah, N., 2014, "An Experimental Implementation of Convolution Encoder and Viterbi decoder by FPGA Emulation", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 3, Issue. 5, May.

- Sh. C., 1948, "A mathematical theory of Communication", Bell Sys. Tech. J., vol. 27 ,pp. 379-423 and 23-656.

- Sh. V. Maiya, Daniel J. Costello and Thomas E. Fuja, 2012, "Low latency Coding; Convolutional Codes versus LDPC", IEEE Transactions on Communications, Vol. 60, No. 5, May.